# Memory Performance of Prolog Architectures

**Kluwer Academic Publishers**

# MEMORY PERFORMANCE OF PROLOG ARCHITECTURES

المنسارات

### THE KLUWER INTERNATIONAL SERIES IN ENGINEERING AND COMPUTER SCIENCE

## FRONTIERS IN LOGIC PROGRAMMING ARCHITECTURE AND MACHINE DESIGN

#### Consulting Editor

Doug DeGroot

'FRONTIERS IN LOGIC PROGRAMMING ARCHITECTURE AND MACHINE DESIGN' is a unique collection of books describing closely related research subjects at the forefront of logic programming architecture and machine design. Initially, the collection will consist of the following books:

# PARALLEL EXECUTION OF LOGIC PROGRAMS by John Conery

### A HIGH PERFORMANCE ARCHITECTURE FOR PROLOG by T. P. Dobry

# INDEPENDENT 'AND' - PARALLEL PROLOG AND ITS ARCHITECTURE by Manuel Hermenegildo

## MEMORY PERFORMANCE OF PROLOG ARCHITECTURES by Evan Tick

John Conery's seminal work at the University of California at Irvine presented the first model for the parallel interpretation of logic programs called the AND/OR Process Model. The same year Conery's work was published , John Warren wrote a landmark paper describing an abstract sequential architecture for Prolog. These two works spawned research efforts throughout the world. One of the largest of these was led by T. P. Dobry at the University of California at Berkeley whose efforts resulted in the design of the Programmed Logic Machine which was the first high-performance Prolog engine. At the same time, at the University of Texas at Austin, Manuel Hermenegildo designed a truly efficient parallel execution model and multiprocessor architecture for logic programming which was the first practical realization of Conery's framework. At Stanford University, Evan Tick designed and measured memory organizations suitable for both Warren's sequential and Hermenegildo's parallel architectures.

This collection of books is designed to provide up-to-date information on Logic Programming Architecture and Machine Design in a timely fashion to researchers and students in the most timely manner possible.

# MEMORY PERFORMANCE OF PROLOG ARCHITECTURES

by

Evan Tick

Stanford University

KLUWER ACADEMIC PUBLISHERS Boston/Dordrecht/Lancaster

#### Distributors for North America:

Kluwer Academic Publishers 101 Philip Drive Assinippi Park Norwell, Massachusetts 02061 USA

#### Distributors for the UK and Ireland:

Kluwer Academic Publishers MTP Press Limited Falcon House, Queen Square Lancaster LAI IRN, UNITED KINGDOM

#### Distributors for all other countries:

Kluwer Academic Publishers Group Distribution Centre Post Office Box 322 3300 AH Dordrecht, THE NETHERLANDS

#### Library of Congress Cataloging-in-Publication Data

Tick, Evan, 1959-Memory performance of prolog architectures / by Evan Tick.

p. cm. — (The Kluwer international series in engineering and computer science; SECS 40. Frontiers in logic programming architecture and machine design)

Bibliography: p. Includes index.

ISBN-13: 978-1-4612-9202-9 e-ISBN-13: 978-1-4613-2017-3

DOI: 10.1007/978-1-4613-2017-3

I. Prolog (Computer program language)

2. Computer architecture.

I. Froidg (Computer program language) 2. Computer architecture. I. Title. II. Series: Kluwer international series in engineering and computer science; SECS 40. III. Series: Kluwer international series in engineering and computer science. Frontiers in logic programming architecture and machine design. QA76.73.P76T53 1987 005.1—dc19

87-26283 CIP

Copyright © 1988 by Kluwer Academic Publishers

Softcover reprint of the hardcover 1st edition 1988

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher, Kluwer Academic Publishers, 101 Philip Drive, Assinippi Park, Norwell, Massachusetts 02061.

For R.K.

المنسارات

# Contents

| Preface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xvii                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Acknowledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | xix                                                                              |

| <ol> <li>Introduction         <ol> <li>What is Prolog?</li> <li>Why Prolog?</li> <li>Reduced Instruction Set Architectures</li></ol></li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                         | 1<br>4<br>8<br>8<br>10<br>10<br>10<br>12<br>12<br>13<br>14                       |

| <ol> <li>Prolog Architectures</li> <li>I. Canonical Prolog Architectures         <ol> <li>Canonical Prolog Architectures</li> <li>I. CIF Data Encoding</li> <li>Cl. CIF Data Encoding</li> <li>Register-Based CIF</li> <li>A Other CIF Metrics: Stability</li> <li>Summary</li> </ol> </li> <li>Environment Stacking Architectures</li> <li>DEC-10 Prolog Abstract Machine</li> <li>Warren Abstract Machine</li> <li>Comparison Between Prolog-10 and WAM</li> <li>Lcode Architecture</li> </ol> <li>Restricted AND-Parallel Prolog Architecture</li> <li>Summary</li> | 16<br>19<br>20<br>22<br>23<br>35<br>41<br>46<br>47<br>49<br>50<br>54<br>61<br>65 |

| <ul> <li>3. Prolog Architecture Measurements</li> <li>3.1. Methodology</li> <li>3.1.1. Compiler</li> <li>3.1.2. Assembler</li> <li>3.1.3. Emulator</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                          | 69<br>70<br>70<br>72<br>72                                                       |

| 3.1.4. Simulators                            | 73  |

|----------------------------------------------|-----|

| 3.2. Benchmarks                              | 73  |

| 3.3. WAM Referencing Characteristics         | 76  |

| 3.3.1. Data Referencing                      | 76  |

| 3.3.2. Instruction Referencing               | 87  |

| 3.4. CIF Referencing Characteristics         | 93  |

| 3.5. PWAM Referencing Characteristics        | 97  |

| 3.6. Summary                                 | 101 |

| 4. Uniprocessor Memory Organizations         | 103 |

| 4.1. Memory Model                            | 105 |

| 4.2. Data Referencing                        | 103 |

| 4.2.1. Choice Point Buffer                   | 107 |

| 4.2.2. Stack Buffer                          | 107 |

| 4.2.3. Environment Stack Buffer              | 115 |

| 4.2.4. Copyback Cache                        | 115 |

| 4.2.5. Smart Cache                           | 121 |

| 4.2.6. Comparison of Data Memories           | 122 |

| 4.3. Instruction Referencing                 | 126 |

| 4.3.1. Instruction Buffer                    | 128 |

| 4.3.2. Instruction Caches                    | 130 |

| 4.4. Local Memory Configurations             | 134 |

| 4.5. Main Memory Design                      | 138 |

| 4.5.1. General Queueing Model                | 139 |

| 4.5.2. Memory Bus Model                      | 145 |

| 4.5.3. Copyback I/D Cache System             | 146 |

| 4.5.4. Stack and Instruction Buffer System   | 152 |

| 4.6. Summary                                 | 157 |

| •                                            |     |

| 5. Multiprocessor Memory Organizations       | 161 |

| 5.1. Memory Model                            | 161 |

| 5.2. The Consistency Problem                 | 164 |

| 5.2.1. Broadcast Cache Coherency             | 166 |

| 5.2.2. Locking in Broadcast Caches           | 167 |

| 5.2.3. Hybrid Cache Coherency                | 168 |

| 5.3. Coherent Cache Measurements             | 172 |

| 5.4. Shared Memory Design                    | 178 |

| 5.4.1. Shared Memory and Bus Queueing Models | 179 |

| 5.4.2. Measurements                          | 183 |

| 5.5. Summary                                 | 191 |

| 6. Conclusions and Future Research           | 193 |

| 6.1. Conclusions                             | 193 |

| 6.2. Future Research                         | 193 |

| 0.2. i uturo itosoaron                       | 190 |

#### CONTENTS

| Appendix A. Glossary of Notation               | 201 |

|------------------------------------------------|-----|

| Appendix B. Lcode Instruction Set Summary      | 205 |

| Appendix C. Local Memory Management Algorithms | 213 |

| References                                     | 217 |

| Index                                          | 225 |

# **List of Figures**

| Figure 1-1:  | Prolog Program Example: isotree/2                  |    |  |  |  |

|--------------|----------------------------------------------------|----|--|--|--|

| Figure 1-2:  | Prolog Program Example: flattenCode/3              |    |  |  |  |

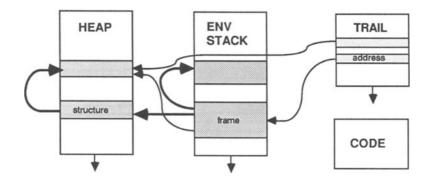

| Figure 2-1:  | Traditional Prolog CIF Storage Model               |    |  |  |  |

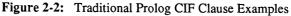

| Figure 2-2:  | Traditional Prolog CIF Clause Examples             | 29 |  |  |  |

| Figure 2-3:  | CIF Instruction Encoding (bits): append/3 Clause 2 | 32 |  |  |  |

| Figure 2-4:  | Traditional CIF Data Referencing (words):          | 33 |  |  |  |

| 8            | append/3                                           |    |  |  |  |

| Figure 2-5:  | Alternative CIF Data Referencing (words):          | 34 |  |  |  |

| 0            | append/3                                           |    |  |  |  |

| Figure 2-6:  | Register-based Prolog CIF Storage Model            | 37 |  |  |  |

| Figure 2-7:  | Register-based Prolog CIF Program Examples         | 39 |  |  |  |

| Figure 2-8:  | CIF Instruction Encoding (bits): append/3 Clause 2 | 41 |  |  |  |

| Figure 2-9:  | Prolog Program Example: Max-N+1 Trails             | 43 |  |  |  |

| Figure 2-10: |                                                    | 43 |  |  |  |

| Figure 2-11: |                                                    | 43 |  |  |  |

| 8            | Into "Head"                                        |    |  |  |  |

| Figure 2-12: | Program Example: WAM/Prolog-10 Comparison          | 51 |  |  |  |

| Figure 2-13: |                                                    | 55 |  |  |  |

| Figure 2-14: |                                                    | 56 |  |  |  |

| Figure 2-15: |                                                    | 56 |  |  |  |

| Figure 2-16: |                                                    | 63 |  |  |  |

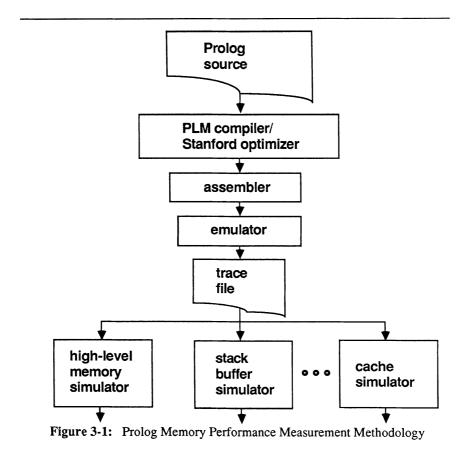

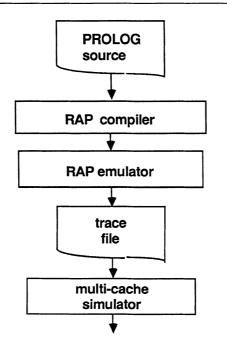

| Figure 3-1:  | Prolog Memory Performance Measurement              | 71 |  |  |  |

| U            | Methodology                                        |    |  |  |  |

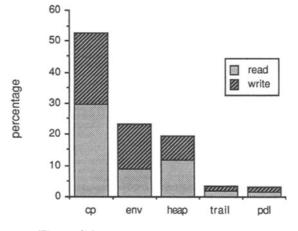

| Figure 3-2:  | Data References By Area                            | 78 |  |  |  |

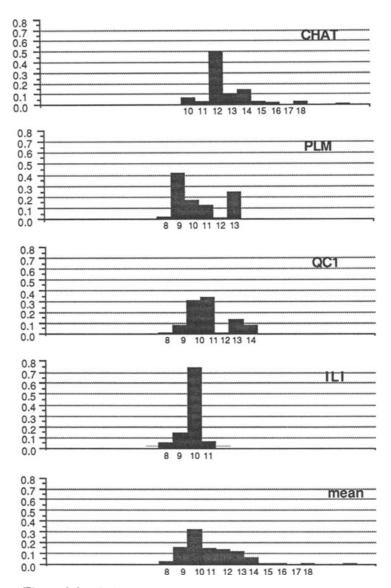

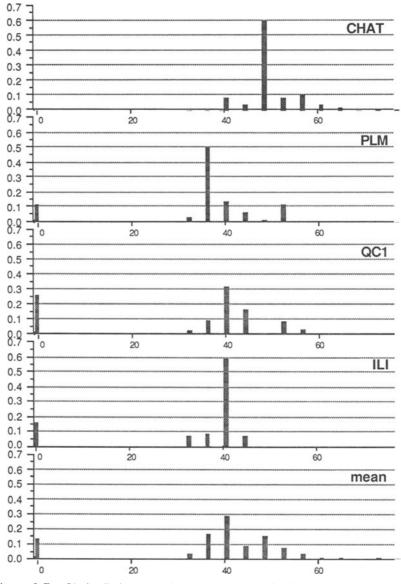

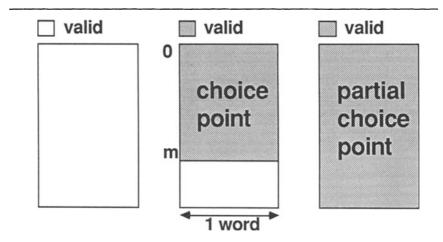

| Figure 3-3:  | Choice Point Size Frequency Distributions (words)  | 82 |  |  |  |

| Figure 3-4:  | Environment Size Frequency Distributions (words)   | 83 |  |  |  |

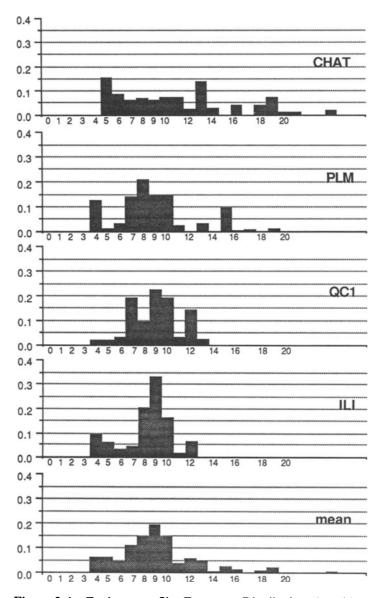

| Figure 3-5:  | Choice Point Depth Frequency Distributions         | 84 |  |  |  |

| -            | (words)                                            |    |  |  |  |

| Figure 3-6:  | Environment Depth Frequency Distributions          | 85 |  |  |  |

|              | (words)                                            |    |  |  |  |

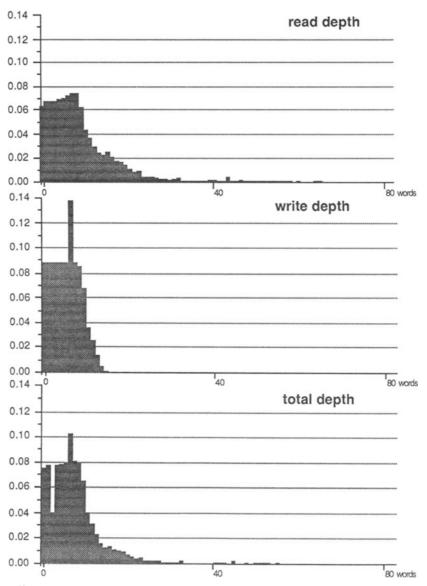

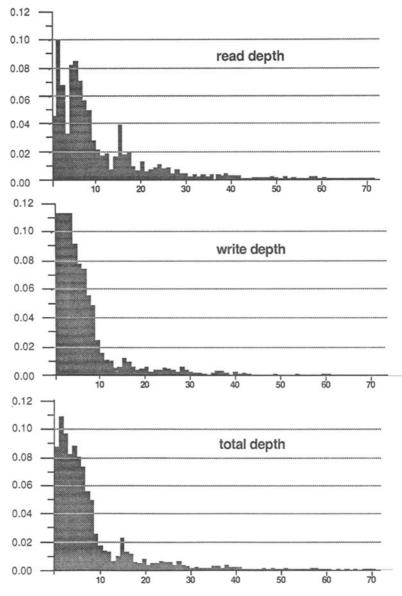

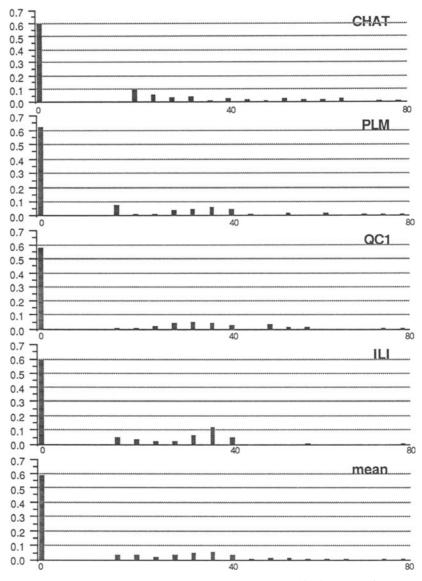

| Figure 3-7:  | Choice Point Reset Depth Frequency Distributions   | 88 |  |  |  |

| -            | (words)                                            |    |  |  |  |

| Figure 3-8:  | Environment Reset Depth Frequency Distributions    | 89 |  |  |  |

| -            | (words)                                            |    |  |  |  |

|              |                                                    |    |  |  |  |

المتسارات

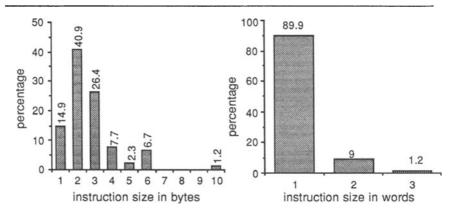

| Figure 3-9: Heap Reset Depth Frequency Distributions (words)<br>Figure 3-10: Dereference Chain Length Distribution<br>Figure 3-11: Instruction Format Distribution | 90<br>91<br>92 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Figure 3-12: RAP-Prolog Performance Measurement<br>Methodology                                                                                                     | 98             |

| Figure 3-13: RAP-Prolog Program Example: Sderiv                                                                                                                    | 99             |

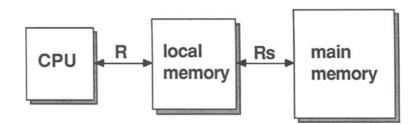

| Figure 4-1: Uniprocessor Memory Model                                                                                                                              | 105            |

| Figure 4-2: Choice Point Buffer Model                                                                                                                              | 108            |

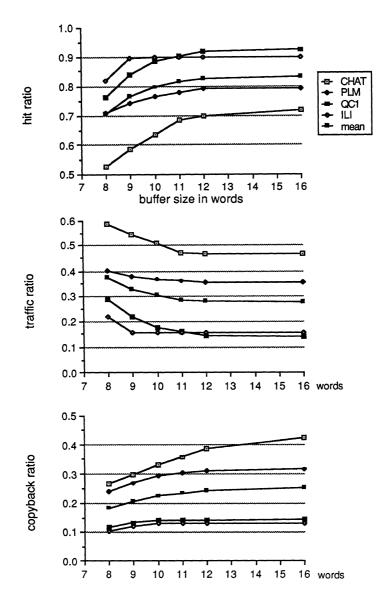

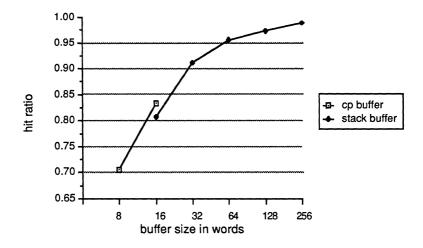

| Figure 4-3: Choice Point Buffer Performance Measurements                                                                                                           | 110            |

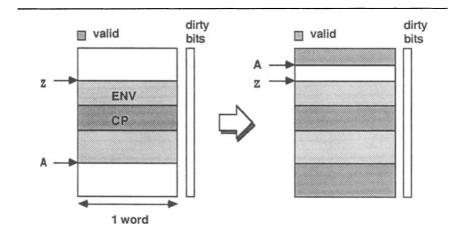

| Figure 4-4: Stack Buffer Model: Object Allocation                                                                                                                  | 111            |

| Figure 4-5: Stack Buffer Performance Measurements                                                                                                                  | 113            |

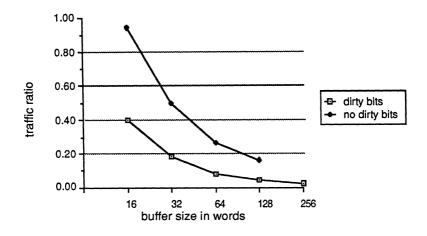

| Figure 4-6: Effect of Dirty Bits on Stack Buffer Traffic Ratio                                                                                                     | 114            |

| Figure 4-7: Choice Point Reference Hit Ratios                                                                                                                      | 114            |

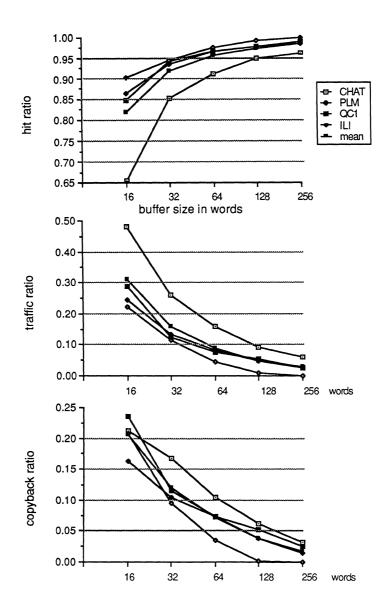

| Figure 4-8: Environment Stack Buffer Performance                                                                                                                   | 116            |

| Measurements                                                                                                                                                       | 117            |

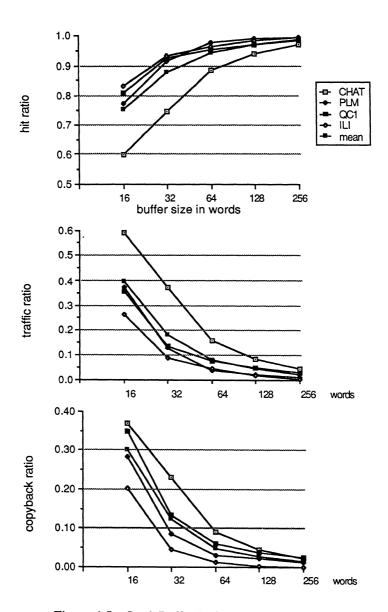

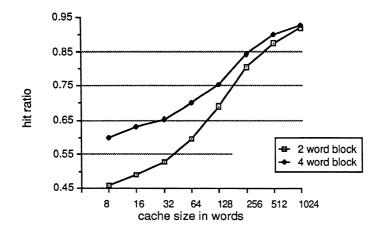

| Figure 4-9: Comparison of Environment Reference Hit Ratios<br>Figure 4-10: Data Cache Performance Measurements                                                     | 117<br>119     |

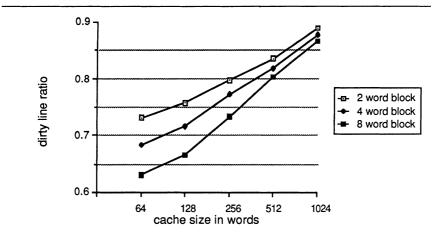

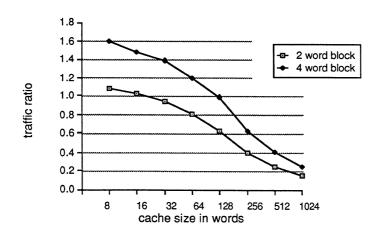

| Figure 4-10: Data Cache Performance Measurements<br>Figure 4-11: Data Cache Dirty Line Ratio                                                                       | 120            |

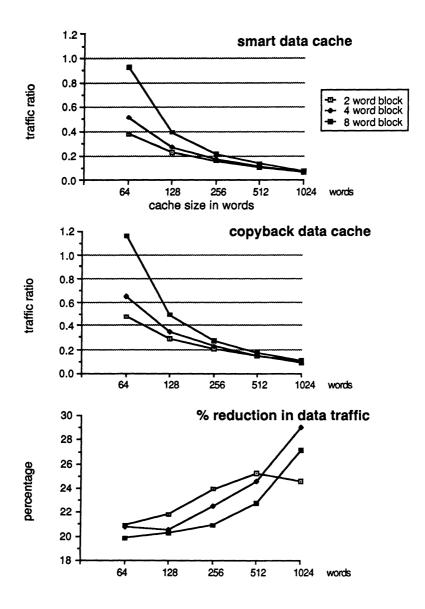

| Figure 4-11: Comparison of Copyback and Smart Caches                                                                                                               | 120            |

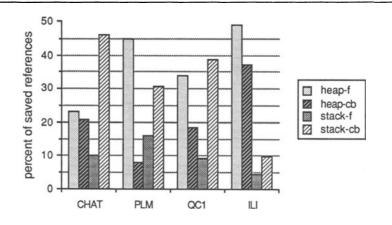

| Figure 4-12: Comparison of Copyback and Smart Caches<br>Figure 4-13: References Saved by Smart Cache                                                               | 123            |

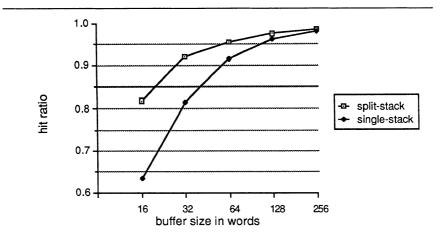

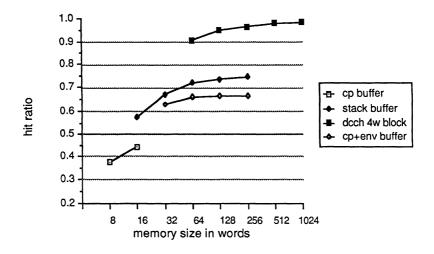

| Figure 4-14: Local Data Memories: Hit Ratio                                                                                                                        | 124            |

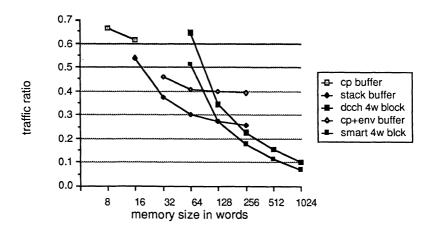

| Figure 4-15: Local Data Memories: Traffic Ratio                                                                                                                    | 125            |

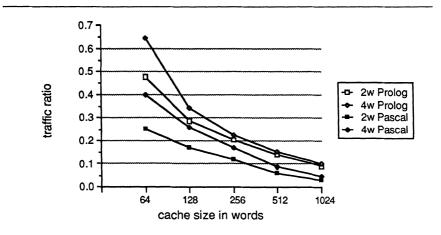

| Figure 4-16: Pascal and Prolog Copyback Data Cache                                                                                                                 | 125            |

| Measurements                                                                                                                                                       | 127            |

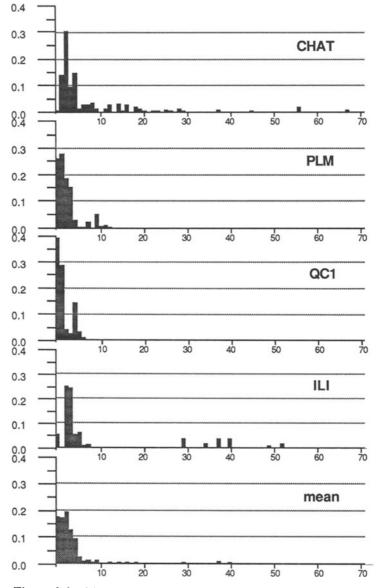

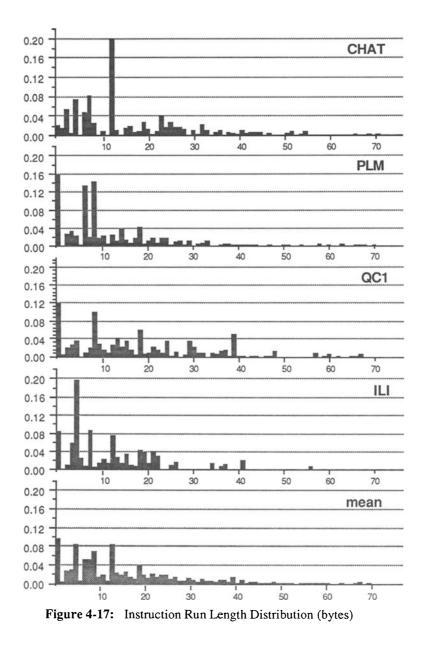

| Figure 4-17: Instruction Run Length Distribution (bytes)                                                                                                           | 129            |

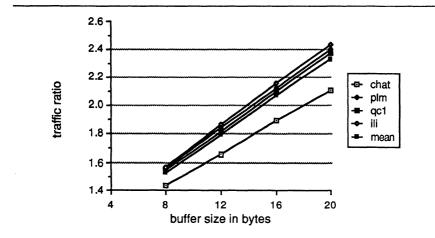

| Figure 4-18: Instruction Buffer Traffic Ratios                                                                                                                     | 131            |

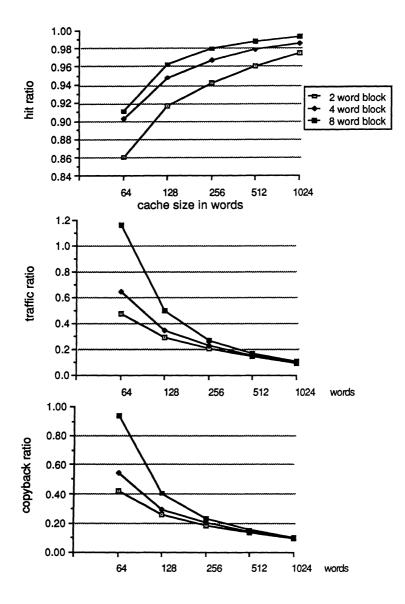

| Figure 4-19: Instruction Cache Hit Ratio                                                                                                                           | 133            |

| Figure 4-20: Instruction Cache Traffic Ratio                                                                                                                       | 133            |

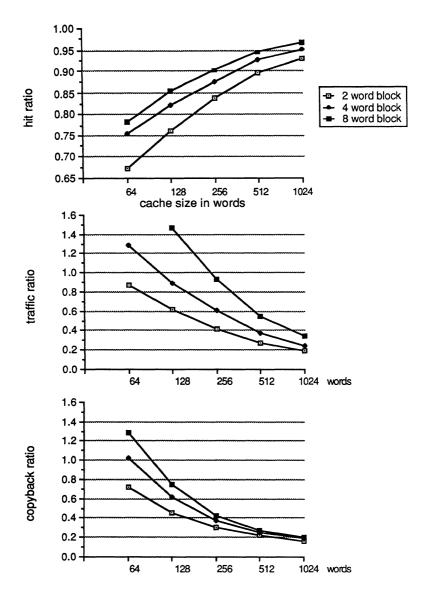

| Figure 4-21: Instr/Data Cache Performance Measurements                                                                                                             | 135            |

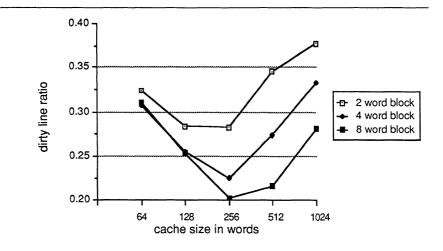

| Figure 4-22: I/D Cache Dirty Line Ratio                                                                                                                            | 136            |

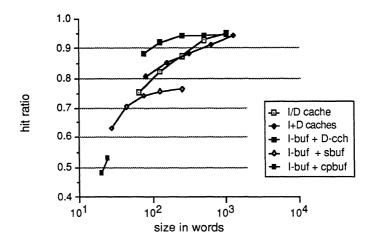

| Figure 4-23: Configuration Hit Ratios                                                                                                                              | 137            |

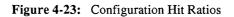

| Figure 4-24: Configuration Traffic Ratios                                                                                                                          | 137            |

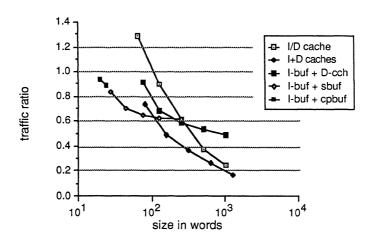

| Figure 4-25: Mean Peak Sustainable Request Arrival Rate                                                                                                            | 142            |

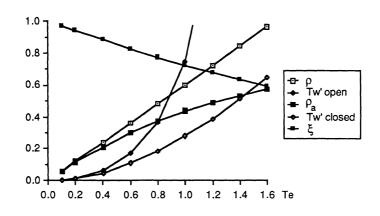

| <b>Figure 4-26:</b> Flores Model ( $\lambda_p = 0.6$ )                                                                                                             | 144            |

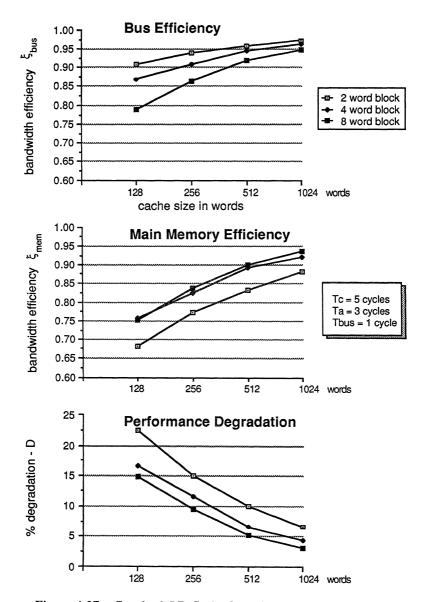

| Figure 4-27: Copyback I/D Cache Queueing Model: 2 Word                                                                                                             | 150            |

| Bus                                                                                                                                                                |                |

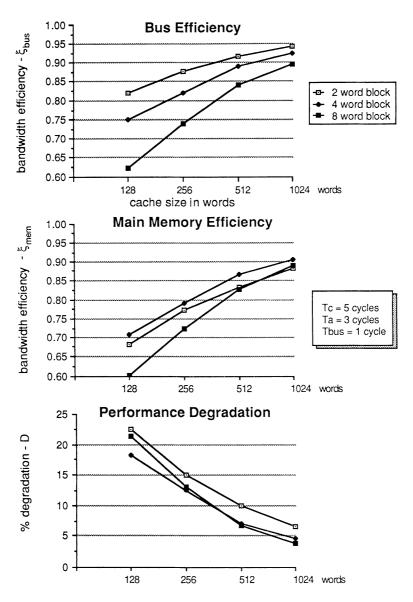

| Figure 4-28: Copyback I/D Cache Queueing Model: 1 Word<br>Bus                                                                                                      | 151            |

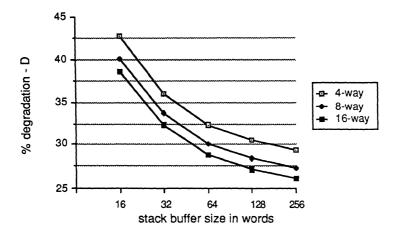

| Figure 4-29: Stack Buffer Configuration: Performance                                                                                                               | 155            |

| Degradation<br>Figure 4-30: Stack Buffer Configuration: Memory Bandwidth                                                                                           | 155            |

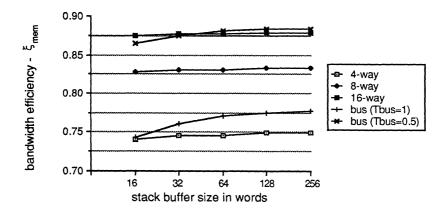

| Efficiency                                                                                                                                                         |                |

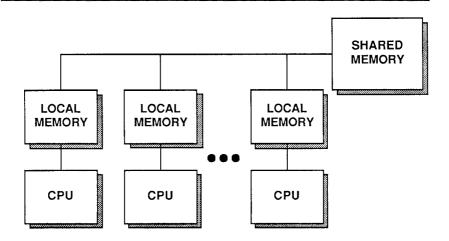

| Figure 5-1: Multiprocessor Shared Memory Model                                                                                                                     | 162            |

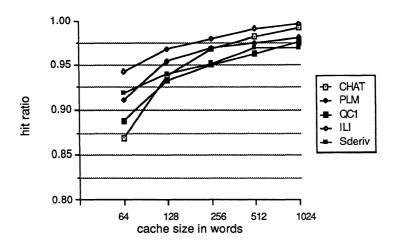

| Figure 5-2: Sderiv Fit: D-Cache (4 word line) Hit Ratio                                                                                                            | 173            |

|                                                                                                                                                                    |                |

المتسارات

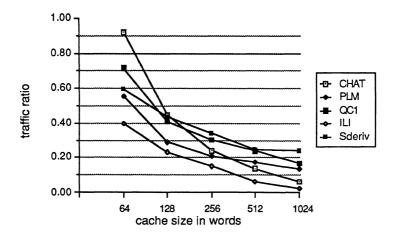

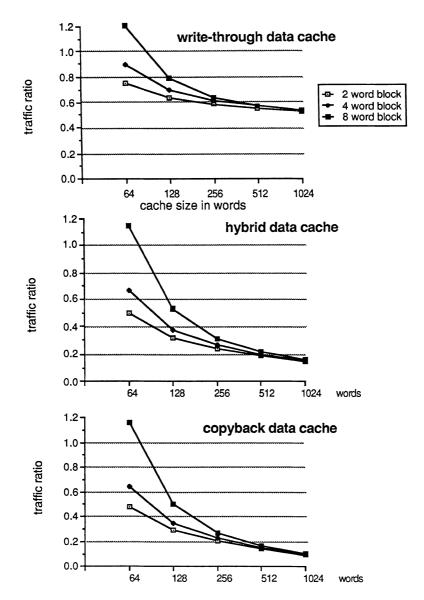

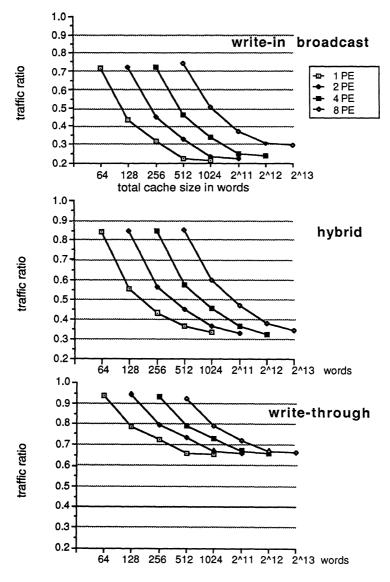

| Figure 5-3:    | Sderiv Fit: D-Cache (4 word line) Traffic Ratio  |     |  |  |

|----------------|--------------------------------------------------|-----|--|--|

| Figure 5-4:    | Data Cache Traffic Ratios: Sequential Benchmarks | 175 |  |  |

| Figure 5-5:    | Sderiv Traffic Ratios of Coherency Schemes for   | 176 |  |  |

|                | Varying #s of PEs                                |     |  |  |

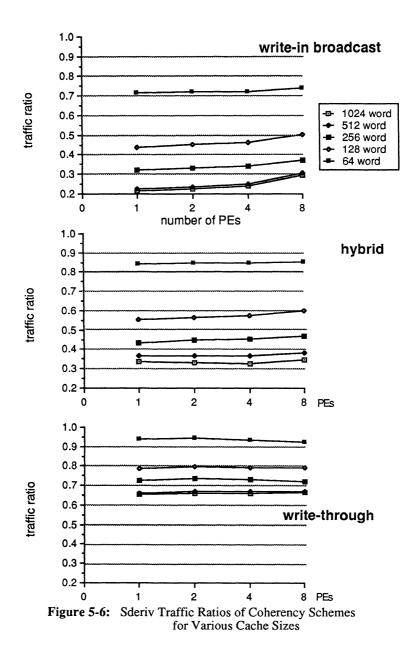

| Figure 5-6:    | Sderiv Traffic Ratios of Coherency Schemes for   | 177 |  |  |

| 0              | Various Cache Sizes                              |     |  |  |

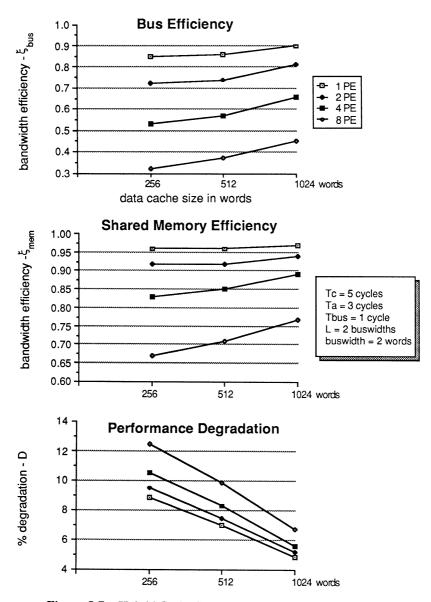

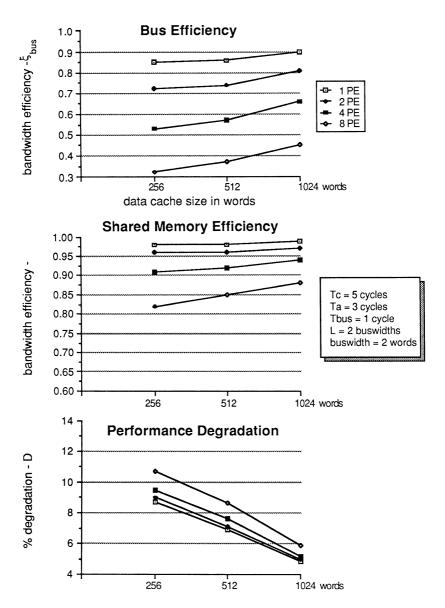

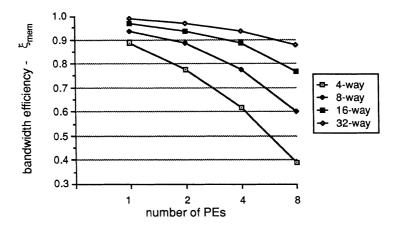

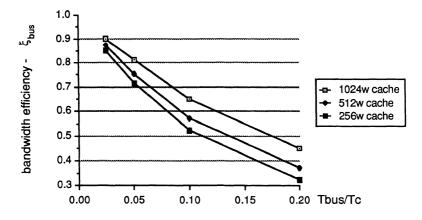

| Figure 5-7:    | Hybrid Cache System With 16-Way Interleaving     | 184 |  |  |

| Figure 5-8:    | Hybrid Cache System With 32-Way Interleaving     | 185 |  |  |

| Figure 5-9:    | Memory Efficiency: 1024 Word Hybrid Cache        | 187 |  |  |

| 8              | System                                           |     |  |  |

| Figure 5-10:   | Percent Performance Degradation: 1024 Word       | 187 |  |  |

| 8              | Hybrid Cache System                              |     |  |  |

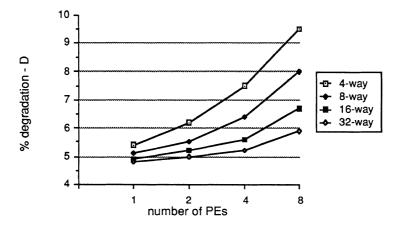

| Figure 5-11:   |                                                  | 189 |  |  |

| 8              | word bus)                                        |     |  |  |

| Figure 5-12:   | Bus Efficiency: 1024 Word Hybrid Cache System    | 189 |  |  |

|                | (2 word bus)                                     |     |  |  |

| Figure 5-13:   |                                                  | 190 |  |  |

| 8              | bus)                                             |     |  |  |

| Figure C-1:    | Choice Point Buffer Management                   | 213 |  |  |

| Figure C-2:    | Stack Buffer Management                          | 214 |  |  |

| Figure C-3:    | Stack Buffer Management Support                  | 215 |  |  |

| Figure C-4:    | E-Stack Buffer Management                        | 215 |  |  |

| 1. igui e C.4. | D-Stack Durier Management                        | 210 |  |  |

# **List of Tables**

| Table 1-1:        | Lisp vs. Prolog: Sun-3/160 Comparison            | 11  |  |  |  |

|-------------------|--------------------------------------------------|-----|--|--|--|

| <b>Table 1-2:</b> | Lisp vs. Prolog: Abstract Machine Comparison     |     |  |  |  |

| <b>Table 2-1:</b> | WAM Model State Registers                        |     |  |  |  |

| <b>Table 2-2:</b> | WAM and Prolog-10 Stack Correspondence           | 52  |  |  |  |

| <b>Table 2-3:</b> | WAM and Prolog-10 Memory Referencing             | 52  |  |  |  |

| <b>Table 2-4:</b> | Prolog-10 - WAM Tradeoffs                        | 53  |  |  |  |

| Table 2-5:        | Lcode Instruction Set                            | 57  |  |  |  |

| <b>Table 2-6:</b> | Lcode Data Object Formats                        | 58  |  |  |  |

| <b>Table 2-7:</b> | PWAM Storage Model (notes 1-7 in text)           | 64  |  |  |  |

| Table 3-1:        | Stanford Emulation Laboratory Prolog Tools       | 70  |  |  |  |

| <b>Table 3-2:</b> | Local Memory Simulators                          | 73  |  |  |  |

| Table 3-3:        | Summary of Prolog Benchmarks' Characteristics    | 75  |  |  |  |

| Table 3-4:        | Runtime Data Areas in Words                      | 76  |  |  |  |

| Table 3-5:        | Data Referencing Characteristics of Benchmarks   | 77  |  |  |  |

| Table 3-6:        | Summary of High-level Prolog Memory Statistics   | 79  |  |  |  |

| <b>Table 3-7:</b> | Heap Reference Depth Statistics (in words)       | 86  |  |  |  |

| <b>Table 3-8:</b> | Instruction References for Benchmarks (per       | 93  |  |  |  |

|                   | Encoding 1)                                      |     |  |  |  |

| <b>Table 3-9:</b> | Comparison Between Prolog CIF Memory             | 94  |  |  |  |

|                   | Bandwidths                                       |     |  |  |  |

| Table 3-10:       | WAM Instruction Bytes Referenced (per CIF)       | 94  |  |  |  |

| Table 3-11:       | Standard (WAM) Indexing Memory Bytes             | 94  |  |  |  |

|                   | Referenced (per CIF)                             |     |  |  |  |

| Table 3-12:       | WAM (De)trailing Memory Bytes Referenced (per    | 94  |  |  |  |

|                   | CIF)                                             |     |  |  |  |

| Table 3-13:       | Data Referencing of Single and Split-Stacks (Per | 96  |  |  |  |

|                   | Single)                                          |     |  |  |  |

| Table 3-14:       | Comparison Between Single and Split-Stack        | 96  |  |  |  |

|                   | Models                                           |     |  |  |  |

| Table 3-15:       | Summary of PWAM Sderiv Benchmark on Four         | 100 |  |  |  |

|                   | PEs                                              |     |  |  |  |

| Table 3-16:       | PWAM Sderiv Data Bandwidth Efficiency            | 100 |  |  |  |

| Table 3-17:       |                                                  | 100 |  |  |  |

|                   | Four PEs                                         |     |  |  |  |

|                   |                                                  |     |  |  |  |

|                   |                                                  |     |  |  |  |

المنسارات

| Table 4-1:PLM Timings1-                                              | 41  |

|----------------------------------------------------------------------|-----|

|                                                                      | 70  |

| <b>Table 5-2:</b> Fit of Sderiv to Large Benchmarks1                 | 74  |

| <b>Table 6-1:</b> Prolog, FORTRAN, and Pascal1                       | 96  |

| <b>Table B-1:</b> Lcode Instruction Set Formats (notes 1-4 in text)2 | 207 |

| Table B-2: Lcode Instruction Reference Characteristics (notes 2      | 209 |

| 1-7 in text)                                                         |     |

| <b>Table B-3:</b> Lcode Characteristics by Type2                     | 211 |

# Preface

One suspects that the people who use computers for their livelihood are growing more "sophisticated" as the field of computer science evolves. This view might be defended by the expanding use of languages such as C and Lisp in contrast to the languages such as FORTRAN and COBOL. This hypothesis is false however — computer languages are not like natural languages where successive generations stick with the language of their ancestors. Computer programmers do not grow more sophisticated - programmers simply take the time to muddle through the increasingly complex language semantics in an attempt to write useful programs. Of course, these programmers are "sophisticated" in the same sense as are hackers of MockLisp, PostScript, and Tex — highly specialized and tedious languages. It is quite frustrating how this myth of sophistication is propagated by some industries, universities, and government agencies. When I was an undergraduate at MIT, I distinctly remember the convoluted questions on exams concerning dynamic scoping in Lisp — the emphasis was placed solely on a "hacker's" view of computation, i.e., the control and manipulation of storage cells. No consideration was given to the logical structure of programs. Within the past five years, Ada and Common Lisp have become programming language standards, despite their complexity (note that dynamic scoping was dropped even from Common Lisp). Of course, most industries' selection of programming languages are primarily driven by the requirement for compatibility (with previous software) and performance. To achieve performance, C and similar languages are based on the functionality of the underlying host machine. As a result, they have no logical structure corresponding to the application.

This socalled trend toward "sophistication" belies a deep-seated problem: computers are simply becoming more difficult to program (contrastingly, the "use" of computers, i.e., pressing buttons, is becoming *easier*, e.g., with the Macintosh). There is nothing wrong with expanding a language to make it more powerful, so long as the expansion is consistent with the basic structure of the language. A language can be extended in directions away from the fundamental basis, if it is ensured that the renegade extensions will very rarely be used, and so

김 للاستشارات

do not confuse the programmer. For example, Lisp has purposefully evolved contrary to this view, as a "ball of mud." In general, implementation issues are a mystery to most programmers (and some implementors), forcing the use of the dirtiest parts of a language in an attempt to gain performance. Often these attempts have no effect or backfire, but they always destroy the logic of a program. In addition, the parallelization of such languages, in an effort to increase performance on multiprocessors, often entails the creation of additional constructs, such as a Future (in Multi-Lisp) or Parallel-Let (in QLisp), with complex semantics which are difficult to use effectively and safely.

Computer programming can benefit from clean, logical program semantics because such semantics facilitate understanding, hence ease of debugging, program modification and high-performance implementation (further arguments can be given concerning program verification, etc.). Logic programming languages are a family of programming languages based on the first-order predicate logic, and manage to retain a semblance of declarative semantics. Although logic programming languages have not yet achieved the ideal plateau of *complete* declarativity, for the most part, the semantics, e.g., of NU-Prolog and CLP( $\Re$ ), are so easy to understand that complex programs can be built with little effort. Recently Prolog has been successfully implemented on multiprocessors, with no need to change its logical semantics. Even within the logic programming community, however, the conflict between performance and clarity (logical interpretation) rages in the arena of parallel implementations. Languages such as GHC and CP sacrifice ease of programming to facilitate implementations on multiprocessors.

This book is concerned with the design and performance of computer architectures, i.e., instruction sets and storage models, for logic programming languages. This book is concerned with the Prolog language because it is commonly used and is representative of a large number of other logic programming languages. Few comments are given as to the relative merits of Prolog as compared to other logic programming languages, or functional languages — that will require an entire other book. Logic programming languages, although far from perfect, are more useable and offer more costefficient multiprocessor implementations than other symbolic programming paradigms. In the future, Prolog will no doubt be extended in many areas, e.g., to include efficient and logical definitions of arrays and modules. Because of the strong logical foundation, ease of programming will be retained and parallel implementations will abound.

المتسارات

# Acknowledgements

Many people deserve acknowledgement for helping me to write this book. Professors Michael Flynn and Stephen Lundstrom of Stanford University have generously shared their knowledge and experience in supporting my research. I am also thankful for the encouragement and assistance of Susan Gere, Leslie Tick, and the colleagues with whom I have worked most closely: Fung Fung Lee, Bill Lynch, Hans Mulder, and Andrew Zimmerman.

At Quintas I have been fortunate to work in an challenging environment created by Lawrence Byrd, William Kornfeld and David H. D. Warren, where many fresh ideas were generated (and stale ones discarded). It has also been a rewarding experience and a great pleasure to work with David Bowen, Tim Lindholm, Brendan McCarthy, Richard O'Keefe, Fernando Pereira, and David Znidarsic.

The "WAM" and "PWAM" architectures discussed in this book are entirely the respective works of David H. D. Warren and Manuel Hermenegildo, to whom both I am greatly indebted. Bill Lynch helped write the WAM emulator described in Chapter 3. Hans Mulder supplied and helped analyze the Pascal data. Philip Bitar, of the University of California at Berkeley, patiently explained cache coherency to me. Manuel Hermenegildo and Richard Warren, of the Microelectronics and computer Technology Corporation (MCC), supplied and helped analyze the PWAM multiprocessor traces. This book was most strengthened by numerous discussions with Fung Fung, Manuel, and Tim.

المستشارات

# MEMORY PERFORMANCE OF PROLOG ARCHITECTURES

المتسارات

# **1** Introduction

The main reason that current computer applications in symbolic processing fail to meet speed constraints on current machines is the gap between the applications and the languages and architectures in which they are implemented. Applications such as natural language understanding and symbolic equation solving, as compared with conventional applications such as numerical modeling and simulation, are further removed from conventional procedural/functional languages such as Pascal and Lisp and their corresponding numeric/scientific processor architectures. This is because these ambitious new applications must, in a sense, be written as *meta-level interpreters*. A meta-level interpreter is a program which performs additional levels of interpretation to implement features not present in the host language, e.g., nondeterminate execution for parsing or a reduction mechanism for theorem proving.

Any approach to improving program performance involves implementing these applications with appropriate languages and designing efficient architectures that either directly correspond to these languages or support interpretation of these features. Features which previously required metainterpretation are now included in the instruction set and are implemented directly in the architecture.

This book presents a study of abstract machine architectures for Prolog, a well-known *logic programming language*. Logic programming is a programming paradigm constructed from the abstract model of first order logic. Prolog is representative of that class of languages with powerful enough functionality to facilitate the development of advanced applications. Prolog is used primarily for artificial intelligence and database applications, as well as general applications such as compiler writing. Prolog differs from procedural languages, such as Pascal and Lisp, in that it is applicative (variables can be bound at most once in an execution path), nondeterminate (alternate paths are executed in an attempt to create a consistent set of variable bindings), and uses

unification (a type of pattern matching) as the primary operation. Thus, means to efficient Prolog execution will likely differ from those of conventional languages.

As the gap between language and architecture decreases, fewer instructions are executed within the program. These instructions do more work and may therefore be more difficult to implement. In most high-level-languagearchitecture machines, the complexity of the instruction set forces a microcoded implementation. An alternative is to implement the abstract machine interpretively on a lower-level host machine. The selection of the most costeffective implementation strategy depends on many considerations technology, instruction set compatibility, design effort, etc. Regardless of the relative weight of each consideration, any design approach requires an understanding of the dynamic Prolog program behavior, i.e., the characteristics of the abstract machine corresponding to Prolog. This book supplies this information.

The problem of increasing Prolog execution speed is approached from the vantage point of memory design. High-speed processors are ultimately limited by memory bandwidth and architectures that require less bandwidth have greater potential for high performance. The memory-referencing characteristics of well-designed abstract machines are minimal in the sense that a host which directly implements the abstract machine instructions as atomic actions will make fewer memory references than other types of hosts. No matter what the host, however, the memory-referencing characteristics measured in this book are, for the most part, applicable.

A family of *canonical* Prolog architectures with advantageous bandwidth requirements is defined in close correspondence to the semantics of Prolog. The Warren Abstract Machine (WAM) architecture [96], used for memory design throughout the book, is a member of this family. Measurements of the Prolog Canonical Interpretive Form (CIF) indicate upper memory-performance bounds afforded by "ideal" attributes (which go beyond the WAM).

High-speed uniprocessor performance is necessary, even within a multiprocessor, because not all types of parallelism exist or can be exploited in all applications. Within a shared memory multiprocessor, local processor memories are necessary to reduce bandwidth and allow undegraded execution of sequential code. The main portion of the book concerns modeling and analysis of two-level memory hierarchies for sequential and parallel Prolog architectures. A trace-driven simulator is used to measure local memories. Sequential Prolog programs are compiled into the WAM instruction set and emulated, producing a memory-address-trace file. Restricted AND-Parallel (RAP) Prolog programs [34] are compiled into the PWAM instruction set [35] and similarly emulated,

assuming a shared memory multiprocessor with a small number of tightlycoupled high-performance processing elements. Main memories are evaluated with asymptotic queueing models.

This book synthesizes logic programming architecture design with the lessons learned from procedural programming architecture design and memory organization. The field of logic programming machine design is new. It is therefore not surprising that little has been published in the area of logic programming machine performance. The vast store of knowledge and folklore available about procedural language architectures and machines is absent for logic programming languages. This book helps fill this gap.

In this book, successive refinements of models of abstraction allow the measurement of the expected memory performance of both sequential and parallel logic programming languages on host processors. The initial level of abstraction is the Prolog source language, leading to canonical interpretive forms (CIFs) for Prolog. These canonical architectures are refined into realizable architectures (Direct Correspondence Architectures — DCAs), such as the WAM and PWAM. Simulations of these architectures executing on a two-level memory model produce memory bandwidth requirement statistics. Refinement of the simple two-level memory model into a queueing model allows the measurement of time dependent statistics, such as processor performance degradation.

At the various levels of abstraction, important results are uncovered. At the architecture level, it is shown that traditional CIF models can be constrained, at little cost in performance, to CIFs more suitable for current technology hosts. The WAM can be viewed as a DCA defined from such a constrained CIF. At the memory simulation level, shallow backtracking is shown to be the primary source of the WAM bandwidth requirement. The analysis of the efficiency of several memory organizations at reducing the bandwidth requirement indicates that caches offer the best memory performance - a result similar to that found for procedural language processors [2]. Less costly memory organizations also perform quite well, a result of the WAM's high locality. At the queueing analysis level, PWAM is shown to exploit parallelism, on a tightly-coupled shared memory multiprocessor, with little overhead with respect to the WAM. It is shown, however, that even for a limited number (eight) of high-performance processing elements, bus capacity is the critical performance bottleneck. This is not to say that shared memory multiprocessors are an inferior design - on the contrary, it is shown that with emerging bus technology and an interleaved shared memory, this type of limited multiprocessor organization can achieve significant speed-ups exploiting Restricted-AND Parallelism alone.

The primary contribution of this book is the successive refinement of

architectures and performance models for logic programming languages, resulting in an accurate description of their dynamic memory-referencing behaviors. A summary of the detailed contributions of the book follows.

- A family of canonical architectures, called CIFs, closely corresponding to Prolog, are described. Measurements of the CIFs are presented, indicating the memory-performance bounds afforded by attributes such as tight instruction-encoding, split-stacks and ideal indexing.

- The memory-referencing characteristics of realistic Prolog programs are determined. Evidence is presented indicating that shallow backtracking is the primary memory-performance bottleneck of environment stacking Prolog architectures.

- Local memories which reduce performance bottlenecks, for various costs, are designed and analyzed. These memories include choice point buffers, stack buffers, copyback data caches, "smart" copyback data caches, instruction buffers, and instruction caches.

- Local memories which solve shared memory multiprocessor consistency problems, specifically for the Restricted AND-Parallel Prolog architecture PWAM, are designed and analyzed. These memories include broadcast, hybrid, and write-through coherent caches. The hybrid cache is a new combination of write-through and write-broadcast cache designs, that takes advantage of RAP-Prolog attributes to guarantee consistency with low overheads and inexpensive hardware.

- Interleaved main memories, for both sequential and parallel architectures, are analyzed with queueing model formulations of the local memories.

In the remainder of this chapter, Prolog is first introduced with examples. Arguments are then given for studying high-level Prolog architectures, as opposed to other alternatives. Lastly, previous work in the fields of architecture design, benchmarking, and memory organization of logic programming languages and machines is reviewed.

### 1.1. What is Prolog?

Prolog is the first practical logic programming language, designed by Colmerauer in 1973 [70], with its theoretical groundwork laid by Kowalski in 1974 [44]. Prolog is the primary representative of logic programming languages — most other logic programming languages are derivatives of the Prolog computation model. To the first order, results of Prolog execution measurements can be extended to Prolog-like languages and logic programming languages in general.

Figure 1-1: Prolog Program Example: isotree/2

Prolog programs and data are composed of *terms*. A term is either a *simple term* or a *compound term* (also called a *complex term* or *structure*). A simple term is either a *constant* or a *variable*. A structure consists of a *functor* and *arguments*. The functor is composed of a *name* and *arity* (this is usually written as *name/arity*). The name is the symbolic identifier of the structure, the arity is the number of arguments, and the arguments themselves are terms. An example of a structure is tree(1,void,Subtree), with functor tree/3. A constant is a structure with zero arity. This may be a number or an atomic identifier. Examples of constants are 1 and void. A (logical) variable is an object which can be bound (only once) to another term. Prolog uses a capitalized identifier to represent a variable, e.g., Subtree.

A Prolog *program* consists of collections of *clauses* known as *procedures*. A clause is a term consisting of a *head* and a *body*. The head contains the formal parameters of the procedure definition. The body consists of a (possibly empty) set of *goals*. A goal is a procedure invocation with its corresponding passed parameters. A procedure is uniquely specified by the name and arity of the head of each of its clauses. The arity of a procedure represents the (fixed) number of arguments it must be passed when invoked.

Figure 1-1 illustrates a program (from [78]) which determines if two trees are isomorphic. The program consists of a single recursive procedure, isotree/2, which has three clauses. The first clause has an empty body and is called a *unit clause* or *fact*. The second two clauses are called *conjunctive clauses*, *non-unit clauses*, or *rules* because they define relations between facts and/or other rules. A third necessary program construct is a *query*, e.g.,

In its simplest form, a query is a procedure invocation with external input, i.e., a request to execute a program with given data.

Prolog semantics can be viewed declaratively or procedurally. The *declarative view* treats a procedure as a logical disjunction of its clauses and a clause as a logical conjunction of its goals. This view benefits programmers. Variables in queries are existentially quantified. For instance, the query given above is read: "Does there *exist* a tree  $\mathbf{x}$  such that the tree represented pictorially below is isomorphic to it?"

Variables appearing in the head of a rule are universally quantified. Variables appearing only in the body of a rule are existentially quantified. For instance, the second clause of **isotree**/2 has an informal declarative reading: "Any two trees are isomorphic if they both have the same value and the left subtree of one is isomorphic to the left subtree of the other and the right subtree of one is isomorphic to the right subtree of the other."

The *procedural view* treats a procedure as an ordered sequence of entry points (clauses) which must be executed until one succeeds. A clause is treated as an ordered sequence of procedure calls (goals), all of which must be executed for success. Upon failure of any goal, the computation is backed up to the entry of the most recently invoked procedure with unattempted clauses. That procedure is re-entered at its next clause and the computation continues. The main implementation distinction between Prolog and procedural languages is that Prolog programs *backtrack* in this manner.

The procedural semantics are derived from the observation that to solve an existential query Q with a universal fact P, one finds a *common instance* C, i.e., two *substitutions*,  $\tau_1$  and  $\tau_2$ , such that  $C = P\tau_1 = Q\tau_2$ . There are two deduction rules in effect here: generalization — an existential query is a logical consequence of an instance of that query, and *instantiation* — an instance of a universally quantified fact is a logical consequence of that fact. The combination of these rules is called *resolution*.

Generalizing, the query Q is a logical consequence of program P with the universal rule  $A := B_1, B_2, ..., B_n$ , if A and Q have a common instance and  $B_1, B_2, ..., B_n$  are also logical consequences of P. This is called *Horn clause resolution*, developed by Robinson [66]. In other words, a goal is executed by attempting resolution with the heads of the clauses of the procedure of the same name and arity as the goal. Successful resolution involves successfully *unifying* each goal argument to each corresponding head argument. Unification finds a *most general* common instance of its input terms to avoid specializing the proof more than necessary.

If the goal cannot match (unify with) any clause of its associated procedure, the goal fails. When the goal matches a clause and it can be determined that no other clauses can match, it is called *determinate execution*. When the goal matches a clause and other (untried) clauses can possibly also match, it is called *nondeterminate execution*.

The scope of a variable is a clause; therefore the occurrences of X in the second and third clauses of isotree/2 in Figure 1-1 are unrelated. The goal isotree(tree(X, void), void) can successfully resolve with the heads of either the second or third clauses. Note again that the scopes of the X in the goal isotree(tree(X, void), void) and the X in the clause heads are independent, and therefore these two variables are unique and can be bound to distinct objects. The goal isotree(void, void) can match only the first clause and the goal isotree(X, Y) can match any clause.

For convenience and efficiency, Prolog has been given additional support for:

- lists a list, which is a structure with functor ./2, is given a special syntax in Prolog. The list '.' (X, Y) can be written as [X|Y]. A list of two objects, '.' (1, '.' (2, [])) can be written as [1,2]. Note that [] is a special constant representing nil (end-of-list). In most tagged Prolog architectures, including the ones considered in this book, the list data type is given a unique tag.

- built-ins many procedures are predefined in Prolog. The most frequently used of these include arithmetic, construction and destruction of terms, conditional tests for types of terms, and strict equality (wherein no unification is allowed to take place).

- cut this is an extra-logical control feature, represented by "!", used to prevent undesired backtracking over the clauses in a procedure. As a goal in a clause of a procedure, cut always succeeds, causing a side effect of disallowing subsequent clauses of that procedure to be tried in the event of backtracking.

As another example, Figure 1-2 shows the most commonly executed Prolog procedure in the QC1 benchmark measured later in this book. The **flattenCode/3** procedure flattens a binary tree structure into a list removing empty sequences represented by the atom **void**, e.g., the query

?- flattenCode((1,(2,3,void,(4,5))),X,[]).

instantiates x to the list [1, 2, 3, 4, 5]. Read procedurally, flattenCode/3 recursively processes the left and right branches of a subtree, using a *difference list* (see [78, p. 239]) to collect the resulting leaves. The second and third arguments of the procedure represent the difference list as an answer list and the tail of the answer list, facilitating efficient concatenation of the resulting sublists from the left and right branches. This method of concatenation is illustrated in the second clause, where the answer is composed by instantiating the tail of the first sequence's flattened list, Code1, to the second sequence's flattened list.

```

flattenCode(void,Code,Code) :- !.

flattenCode((Seq1,Seq2),Code0,Code) :- !,

flattenCode(Seq1,Code0,Code1),

flattenCode(Seq2,Code1,Code).

flattenCode(Instr,[Instr|Code],Code).

```

Figure 1-2: Prolog Program Example: flattenCode/3

Read declaratively, flattenCode/3 specifies three rules concerning flattening. The result of flattening an empty sequence is an empty difference list. The result of flattening a binary tree, (Seq1, Seq2), is Code0 (with tail Code), if flattening the left subtree, Seq1, results in Code0 (with tail Code1) and flattening the right subtree, Seq2, results in Code1 (with tail Code). The result of flattening anything else, Instr, is a list with head Instr and tail Code.

### 1.2. Why Prolog?

This book discusses how to make Prolog programs execute quickly. In this section the selection of Prolog as a target language, and a high-level Prolog architecture as a target instruction set, are justified. Three arguments are given: for designing complex instruction architectures over reduced instruction architectures, for analyzing Prolog instead of a committed-choice nondeterminism logic programming language, and for choosing Prolog over Lisp, a popular functional language.

### **1.2.1. Reduced Instruction Set Architectures**

An alternative approach to increasing the execution speed of logic programs is to translate the high-level architecture into a lower-level target or *host* instruction set. For instance this host can be a *reduced instruction set computer* (RISC) [63, 61, 81]. The goal of reduced instruction set machines is to simplify the instruction set, allowing more effective compiler optimizations and streamlined hardware. For the most part, results of this book are applicable for *any* host. Exceptions are results concerning instruction referencing

characteristics. In the case of instructions, a microcode implementation of a high-level architecture cannot be easily compared to a reduced instruction set architecture.

Reduced instruction set architectures were originally designed for current hardware technology, procedural languages and general purpose applications. It is argued here that such architectures are not necessarily as well-suited to advanced hardware technology and symbolic processing applications, as are high-level instruction set architectures. First instruction referencing, then data referencing characteristics are considered.

Given advanced (denser) hardware, the benefit of a reduced instruction set and a corresponding necessarily large instruction cache is not clearly superior to a complex instruction set and a corresponding necessarily large micro-store. Prolog code, when compiled into a reduced instruction set, expands to a size incompatible with current on-chip (reduced instruction set machine) instruction caches. Borriello et al. [8] report that to achieve similar miss ratios, SPUR, a reduced instruction set microprocessor [81], requires significantly larger caches than would the PLM, a microcoded complex instruction set machine [21].

General purpose applications and procedural languages have certain attributes, such as high locality, not shared by symbolic processing applications and applicative languages. For example, in this book (Section 4.2.6), it is found that for a 1024 word copyback data cache (with a four word line size), typical Prolog programs display four times the traffic ratios of typical Pascal programs. Most reduced instruction set machines rely on high locality to allow their pipelines to operate efficiently. The specialization of the architecture, to incorporate attributes such as tags (e.g., SPUR) and shadow registers (e.g., Pegasus [71]), is necessary to reduce the data bandwidth requirement.

The critical resource is the available on/off chip bandwidth. The gap between Prolog and conventional RISC architectures is so great as to make the available chip bandwidth intolerable. Complex instruction set architectures, specialized for Prolog, reduce the gap to a reasonable level, thereby reducing the bandwidth requirement.

These arguments aside, assume that a reduced instruction set host can be made to execute Prolog programs faster than a microcoded implementation of a high-level architecture. Raw speed of compiled, optimized programs does not in itself solve the *software crisis*. The software crisis refers to the growing complexity and cost of *developing* applications. High-level architectures allow the use of relatively simple (and therefore fast) compilers. In addition, decompilation for symbolic debugging is facilitated by high-level architectures. The application development cycle involves multiple recompilations, as well as debugging of code. Both of these activities are supported by a single high-level

architecture host. Although two different machines can be used for the purposes of application development and delivery, this is not a reasonable solution except for the largest commercial applications.

### **1.2.2. Parallel Logic Programming Languages**

Parallel logic programming languages are of considerable interest for attaining high performance on future multiprocessors. Gupta et al. [33] and others have shown, however, that unlimited parallelism does not exist in many application programs. Therefore, as with conventional multiprocessors, one performance bottleneck will be the speed of sequential execution of a single processing element.

Many parallel logic programming languages are based on *committed-choice nondeterminism*, wherein once a clause head (and an extension to the head, called the *guard*, consisting of simple goals) succeeds, the procedure commits to that clause and will not backtrack. This weakening of the logic programming paradigm once again increases the gap between the application and language. In addition, the storage models required by committed-choice languages cannot be implemented as efficiently on sequential processors as sequential languages, such as Prolog. Committed-choice-language architectures are based on the hypothesis that the *amount* of parallelism uncovered by the language will outweigh any inefficiencies incurred in single processor execution.

There is no doubt that multiprocessor execution is of the *utmost importance* in increasing logic programming performance. The view taken in this book is in agreement with Butler et al. [11], Hermenegildo [35], and others, who propose parallel architectures for Prolog built around an efficient *sequential* architecture, i.e., storage model. These architectures are based on the hypothesis that the efficiency of single processor execution outweighs the restricted amount of parallelism uncovered by the language. Local and shared memory design and modeling for one such parallel architecture are presented in this book.

#### 1.2.3. Lisp

Lisp, a symbolic language based on function application [51, 77], is both more popular and more mature than Prolog. Studies of Lisp architecture performance have been conducted [29] and Lisp machines built (e.g., Symbolics 3600 [80], SPUR [81]). There are two primary deficiencies with Lisp as

| program | Sun<br>Common Lisp† | Quintus<br>Prolog‡ | Lisp:Prolog |

|---------|---------------------|--------------------|-------------|

| Boyer   | 15.08 sec           | 25.50 sec          | 0.59        |

| Deriv   | 4.24 sec            | 6.30 sec           | 0.67        |

| Puzzle  | 8.44 sec            | 2.43 sec           | 3.47        |

| Tak     | 0.47 sec            | 4.59 sec           | 0.10        |

| ± .• •  |                     |                    |             |

† native code

‡ emulated byte-code

Table 1-1:

Lisp vs. Prolog: Sun-3/160 Comparison

compared with Prolog — both stemming from the evolution of Lisp (e.g., to Common Lisp). Lisp programs, as written by most programmers (see, for instance, the benchmarks presented in Gabriel [29]), have no declarative reading, and are not applicative. The first deficiency reduces the reliability, readability and extensibility of Lisp programs. The second deficiency reduces the ability to parallelize a Lisp program, either automatically or by the programmer. Although these arguments are common in the literature, here a third argument is introduced.

It is argued below, with evidence presented in Tick [83], that as a result of increased functionality (over Lisp), Prolog holds more promise than Lisp for *future* high-speed processors. Studies of Prolog performance as compared with Lisp [59, 92] have been favorable to Prolog. In Tick [83] evidence is given that Prolog has greater *semantic content* than Lisp. Two results are given based on the assumption that memory bandwidth is the ultimate performance measure.

The first result is that Lisp is better mapped onto current machines than Prolog. This is tenuously supported by comparisons between commercially available Lisp and Prolog systems, executing a subset of the Gabriel benchmarks as shown in Table 1-1. Although "apples vs. oranges," comparing these implementations serve to indicate that Lisp runs faster than Prolog on hardware with a limited number of state registers. Whether Prolog can reach Lisp performance on conventional machines is primarily dependent on how much of the Prolog state can be contained in available state registers, and if Prolog compilers of the same level of sophistication as those used for Lisp can be built.

The second result is that Prolog has a greater potential to exploit the additional state and state transfers advanced hardware can offer. The high semantic content or *potency* of a language is indicated, for a given program, by a high mean number of memory references per instruction executed and a low total number of instructions executed. From the statistics shown in Table 1-2, Prolog

0.30

1.29

1.60

1.18

|                 | Tak    |        |            | Boyer    |              |  |

|-----------------|--------|--------|------------|----------|--------------|--|

|                 | Lisp   | Prolog | L/P        | Lisp     | Prolog L/P   |  |

| instructions    | 683792 | 811008 |            | 9093949  | 4011264      |  |

| data ref        | 667891 | 508865 | 1.31       | 8200807  | 5752632 1.43 |  |

| instr ref       | 747401 | 938226 | 0.80       | 12078345 | 4555707 2.65 |  |

| data ref/instr  | 0.97   | 0.63   |            | 0.90     | 1.43         |  |

| instr ref/instr | 1.09   | 1.16   |            | 1.33     | 1.14         |  |

|                 | Deriv  |        | Pu         | zzle     |              |  |

|                 | Lisp   | Prolog | <u>L/P</u> | Lisp     | Prolog L/P   |  |

| instructions    | 598    | 277    |            | 12172280 | 525650       |  |

| data ref        | 515    | 537    | 0.96       | 3711662  | 842468 4.41  |  |

| instr ref       | 708    | 366    | 1.93       | 15759345 | 617679 25.5  |  |

| <b>Table 1-2:</b> | Lien ve  | Drology | Abstract | Machina   | Comparison |

|-------------------|----------|---------|----------|-----------|------------|

| 1 able 1-2:       | LISD VS. | Prolog: | ADSITACE | iviacnine | Comparison |

displays greater potency than Lisp because the functionality of backtracking and unification are integrated into Prolog and its architecture.

In summary, to reduce the execution time of a given application, one wishes to both

• reduce the gap between the architecture and the language.

1.94

1.32

• increase the semantic content of the language, increasing its performance potential.

As shown, available hardware and compiler technology constrains these criteria, currently favoring Lisp. Future technology may well favor Prolog.

# **1.3. Previous Work**

data ref/instr

instr ref/instr

0.87

1.19

# 1.3.1. Architectures

Flynn and Hoevel [27, 26] derived the theory of ideal language machines for FORTRAN. Wakefield [91] implemented this theory by designing and measuring ADEPT, a direct correspondence architecture (DCA) for Pascal. This book extends these concepts from procedural languages to applicative, logic programming languages, specifically Prolog. The step to Prolog is much larger than from FORTRAN to Pascal, because of attributes such as single-assignment,

nondeterminism, pointers, and unification. The singular contribution of the ideal Prolog architecture is the inclusion of a two-level name space (registers and memory), displaying superior memory-referencing characteristics under assumptions of a less costly host.

Sequential Prolog architectures designed by D.H.D. Warren [93, 96], Byrd [9], and Bowen [10] are called *environment-stacking* architectures. These models utilize a stack holding local procedure variables in frames called *environments*. These architectures have been designed in the traditional manner, as evolutionary improvements from interpreter to compiler to abstract machine model. A contribution of this book is to show how the theory of ideal language machines is another equally valid design methodology, resulting in the same high-performance Prolog architectures.

PWAM, designed by Hermenegildo [35], is an AND-parallel Prolog extension of the WAM. The PWAM model extends the initial work in Restricted AND-Parallelism by DeGroot [18], by developing an efficient architecture with a viable backtracking semantics. A contribution of this book is the measurement of the memory-referencing characteristics of PWAM executing on a shared memory multiprocessor. It is shown that PWAM's memory efficiency compares well with the WAM for sequential code and that PWAM has low communication overheads for parallel code.

### **1.3.2.** Benchmarking

Many studies of both the static and dynamic characteristics of Prolog programs have been undertaken. Warren [93] measured the execution time of small Prolog programs to compare the performance of DEC-10 Prolog with the performance of various other programming languages. This was one of the first sets of Prolog benchmarks published with performance measurements. Wilk [98] measured the execution time of small, synthetic Prolog programs to compare different systems. He discusses the important attributes of a Prolog system, ranging from garbage collection to debugging capabilities.

Ross [68, 69] measured the memory-referencing behavior of small sequential Prolog programs. In contrast to this book, he studied the Prolog working set, i.e., page referencing characteristics, between main memory and backing store. Prolog was found to have a larger working set than typical C programs. A Prolog paging strategy was designed which avoids transferring pages not belonging to the current valid storage areas (as defined by stack pointers, etc.). For compiled programs, this reduced page traffic by a factor of two over a conventional paging strategy.

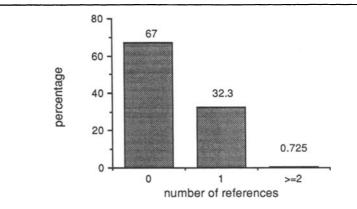

Matsumoto [50], Ratcliffe [64], and Onai [60] performed static analysis of large Prolog programs (including versions of the CHAT and PLM benchmarks used in this book). They measured several attributes such as the number of cuts per clause, and the number and type of built-in goals per clause. These high-level statistics were aimed at evaluating compiler techniques, but not at directly analyzing the performance of the programs. Since static code was measured, these statistics don't necessarily reflect runtime behavior. Nor were these high-level analyses based on architecture models, as is done in this book.

Ratcliffe measured parallelism metrics from static benchmarks to determine the amount of potential concurrency. Onai also measured parallelism metrics from two dynamic benchmarks. These high-level analyses were also not based on architecture models. Dobry [21], however, measured the execution time and simple memory-referencing characteristics of small Prolog programs, to illustrate the effectiveness of the PLM architecture. This work was extended by Touati [86] to include several larger benchmarks, including versions of the CHAT and ILI benchmarks used in this book. Touati's study presents measurements of detailed high-level characteristics of the PLM, such as cdr-coding efficiency, with the aim of evaluating compiler optimization strategies. Many of the results presented confirm those in this book. Note that although the PLM was built, the studies cited above used simulation for their measurements.

Hermenegildo [35] measured the performance characteristics of small, synthetic benchmarks to illustrate the effectiveness of the PWAM architecture. His analysis assumed an idealized shared memory organization and emphasized high-level-architecture characterization. This book extends this work by analyzing PWAM memory-referencing characteristics assuming a realistic shared memory multiprocessor organization.

### 1.3.3. Memory Organization

A few comparative sequential Prolog hardware studies have been conducted [8, 54, 31] and several Prolog machines built [41, 57, 58, 56, 21, 71]. The Kobe University PEK machine [41] compiles Prolog into horizontal microcode that is executed from a writable control store (WCS). The PEK architecture is similar to that of DEC-10 Prolog [93]. In addition to a 16K (by 96 bit) WCS, the PEK also incorporates a 4K (by 34 bit) stack buffer, 16K (by 34 bit) heap buffer, and 16K (by 14 bit) trail buffer.

The ICOT High-speed Prolog Machine (HPM or Chi) instruction set is a derivative of the WAM [57]. The HPM incorporates an 8K (by 36 bit), 4-way set associative write-through I/D cache. Two ICOT Personal Sequential Inference

(PSI) machines have been designed. The PSI-I [58] is a microcoded interpreter for KL0, a simple compiled form of Prolog. PSI-I is equipped with an 8K (by 40 bit), 2-way set associative copyback I/D (combined instruction, data) cache. The PSI-II [56] instruction set is a derivative of the WAM. It incorporates a 4K (by 40 bit), directly mapped copyback I/D cache. The PSI-II incorporates a "write stack" operation which avoids fetching the next (invalid) word at the top of stack. This is a limited example of the more general "smart cache" described and analyzed in this book.

The UC Berkeley Programmed Logic Machine (PLM) is a pipelined, microcoded Prolog machine [21, 20]. The machine instruction set is a derivative of the WAM. The PLM incorporates a fixed-size single choice point buffer, a look-ahead instruction buffer, and a write buffer (to queue outstanding write requests). The X1 [22], a version of the PLM built by Xenologic Inc., includes two directly mapped 64K (32 bit) word caches (separating instructions and data) without the choice point buffer. The local memories simulated in this book are smaller (up to 1024 32-bit words) than those in the machines previously described. The intention is to model local memories that can be integrated with the CPU.

The Mitsubishi Pegasus is a pipelined, RISC microprocessor for Prolog [71]. The tagged, load/store architecture incorporates a *shadow register set*, similar to that suggested in this book. Measurements made of small benchmarks running on Pegasus indicated that the shadow registers can improve program performance by up to 17% [71].

The Hitachi IPP [1] is a pipelined, microcoded Prolog machine. The instruction set is a derivative of the WAM. The IPP incorporates a four word instruction prefetch buffer, write-through cache, and write buffer. Processor performance has been simulated for small programs, indicating that advanced indexing techniques and global register allocation can give speedups of up to 3.4 times that of unoptimized code. Optimizations similar to these are discussed in Chapter 2.

Borriello et al. [8] described and measured the execution of Prolog on SPUR, a microprocessor with a tagged RISC architecture. 14 small Prolog benchmarks were executed on the SPUR and PLM simulators, allowing comparison of execution cycles. The results indicated that number of SPUR cycles executed was 2.3 times that of the PLM. The number of SPUR instructions executed was 16 times greater than the PLM. Borriello concludes that assuming similar memory configurations for PLM and SPUR, the SPUR can achieve 66% of PLM performance, if minor tag modifications and compiler improvements are made to SPUR.

Mulder and Tick [54] described and measured the execution of Prolog on an

MC68020 microprocessor. Approximation methods were used to compare PLM and MC68020 execution cycles for three large benchmarks (the instruction frequencies presented in Appendix B of this book were used to estimate the number of execution cycles). The results indicated that assuming equivalent main memory speeds, the number of MC68020 cycles executed was 2.5 to 3.5 times that of the PLM.

Gee, et al. [31] microcoded a VAX 8600 general-purpose computer to directly emulate WAM instructions. They found that 85% of the PLM execution performance could be obtained for simple benchmarks. Because a general-purpose host was used, high-performance numeric computation was also achieved.

Studies in memory organizations for high-level procedural language architectures include the works of Alpert [2] and Mitchell [53]. Alpert described and measured the data memory performance of *contour buffers* and copyback data caches for Pascal architectures. The contour buffer is similar in function to the stack buffer presented in this book. Alpert's cache simulator is used here to make uniprocessor copyback cache measurements, and has been extended to model write-through caches. Mitchell described and measured instruction cache performance for a wide range of architectures. Pascal benchmarks were simulated, providing performance metrics with which to compare architectures.

Cache studies for traditional architectures are numerous. Most heavily referenced in this book are works by Smith [75], Bitar [6], Archibald [3], and Hill [38]. Smith and Hill present detailed studies of uniprocessor cache design and performance. Bitar and Archibald present detailed studies of multiprocessor (coherent) cache design and performance. This book extends these studies by analyzing cache performance for logic programming language architectures.

# 1.4. Book Outline

This book assumes familiarity with Prolog (refer to [78] for instance). Detailed knowledge of the WAM and PWAM instruction sets are *not* necessary. These architectures are reviewed in the Chapter 2, although the interested reader is referred to Warren [96] and Hermenegildo [35], respectively, for complete details.

The body of this book contains four parts. The first part, Chapter 2, describes a family of Prolog architectures defined from the principles of canonical high-level language architectures. Prolog Canonical Interpretive

Forms (CIFs) are introduced which have attributes with certain "ideal" qualities not present in the WAM. The WAM is introduced from a historical perspective of DEC-10 Prolog and its variants. PWAM, chosen for later multiprocessor performance measurements, is also reviewed.

Chapter 3 presents the tools and benchmarks used to make empirical measurements of memory models introduced in Chapter 4. The WAM, Prolog CIFs, and PWAM memory-referencing characteristics are presented and compared.

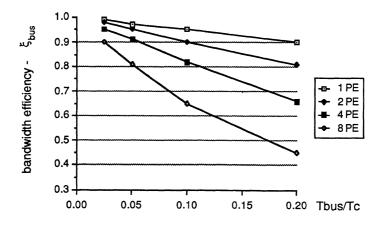

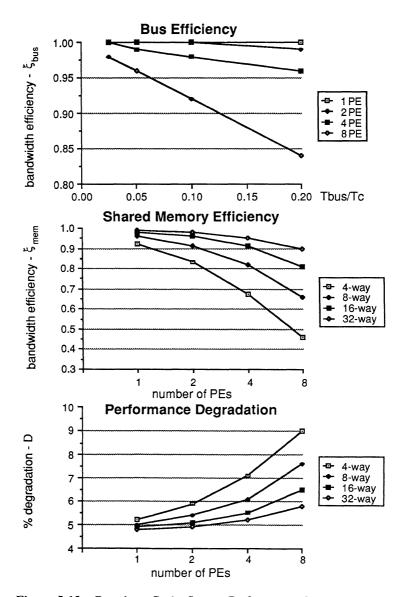

Chapter 4 presents two-level memory hierarchies well-suited for sequential Prolog architectures. Local memory models are described and measurements are presented. The local memory designs are generalized into parameterized queueing models for main memory design. These models are evaluated, giving the *bandwidth efficiency* of both the main memory and the memory bus, and the expected processor *performance degradation* due to the local memory miss penalties, aggravated by main memory contention.

Chapter 5 presents memory hierarchies well-suited for parallel Prolog architectures, specifically PWAM. Shared memory multiprocessor consistency problems for PWAM are outlined and local memory models are presented which solve these problems. The queueing models previously introduced are extended to describe shared memory multiprocessors.

Finally, Chapter 6 presents conclusions drawn from the research and points to directions for future research.

المنسارات

# **2** Prolog Architectures

This chapter describes a family of high-level instruction set architectures for the Prolog language. The Prolog architecture family is *canonical*, i.e., it is defined from the semantics of Prolog in the tradition of Flynn and Hoevel's work on canonical architectures for procedural languages [27]. The most notable member of the Prolog architecture family is the Warren Abstract Machine (WAM) architecture [96], currently implemented on general purpose hosts via native-code (e.g., Tricia [14]), interpretation (e.g., Quintus Prolog [62]), microcoded interpretation (e.g., on the VAX 8600 [31]), and on dedicated hosts (e.g., the UC Berkeley Programmed Logic Machine (PLM) [21] and the ICOT PSI-II [56]).

The canonical Prolog architecture family includes attributes such as *ideal indexing* (a model for directly selecting the correct procedure entry point in a nondeterministic procedure invocation) and tight instruction encoding. Although not all of these attributes are realizable, they indicate upper bounds on sequential execution performance. In addition, they can be used *constructively* to aid in the design of realizable architectures on current hosts. It is shown that the WAM is such an architecture, i.e., the WAM instruction set closely corresponds to the Prolog source language. Results are presented indicating the extent to which the WAM achieves the canonical measures.

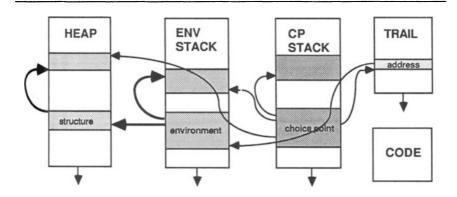

An alternative introduction to the WAM architecture is also presented by means of its historical ancestor, the DEC-10 Prolog abstract machine (Prolog-10) [93]. These two architectures are compared in the area of memory performance. Evidence is presented suggesting that the WAM achieves its goal of optimizing the execution of determinate code (with respect to Prolog-10), at the cost of slower nondeterminate execution. The performance difference (in terms of memory references made) is greatest for shallow backtracking programs.

Finally, an overview of the Restricted AND-Parallel Prolog architecture (PWAM) [35] is given. In the next chapter, memory-referencing characteristics

🚺 للاستشارات

of these architectures are presented and the relative merits of their attributes are compared.

## 2.1. Canonical Prolog Architectures